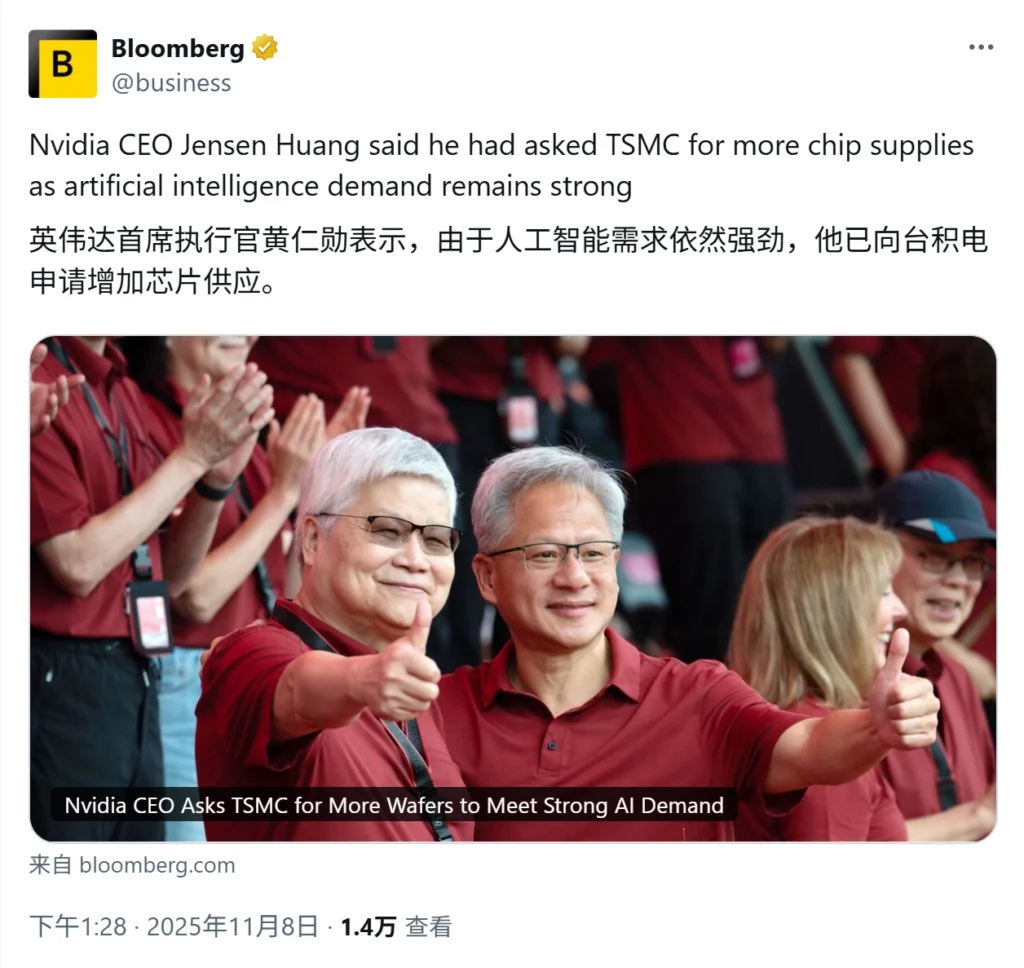

El CEO de Nvidia, Jensen Huang, visitó recientemente el campus de TSMC en Hsinchu (Taiwán) para participar en los juegos deportivos de la compañía, un evento interno que nunca antes había abierto a clientes externos en 38 años. En ese escenario, Huang dedicó un discurso memorable a más de 20.000 empleados de TSMC, destacando su vínculo con la fundición y afirmando sin pelos en la lengua: “Sin TSMC, no habría Nvidia”.

Este acto —y sus declaraciones— adquieren mayor peso si lo ponemos en contexto técnico: estamos ante la columna vertebral de la IA moderna, con una empresa que lidera el hardware y otra que es la fábrica más avanzada del planeta. Pero vayamos por bloques, porque hay mucho que rascar.

La arquitectura Blackwell: mucho más que una GPU

– Diseño y proceso de fabricación

- Blackwell está fabricada mediante el proceso TSMC 4NP (una versión personalizada del 4 nm de TSMC) para uso en centros de datos. En su lanzamiento, Nvidia afirma que sus GPU Blackwell interiorizan 208 000 millones de transistores en total (estructura dual de dies), gracias a un diseño con dos dados “reticle-limit” unidos para funcionar como un solo chip.

- En la variante de consumo se habla de nodos TSMC 4N, más conservadores, lo que indica que Nvidia apostó por estabilidad en lugar de “solo” reducir nodo para la versión desktop.

– Arquitectura interna

- Blackwell integra una gran cantidad de “Streaming Multiprocessors” (SMs), tensor cores, RT cores, etc. Por ejemplo, según la hoja técnica de Nvidia: “GB202 GPU incluye 12 GPCs, 96 TPCs, 192 Streaming Multiprocessors…”

- El nuevo chip hace hincapié no solo en cálculo en coma flotante (FP32, FP16) sino en formatos más agresivos para IA (BFLOAT16, INT4/INT8) e integra un gran ancho de cache L2 para reducir latencias de memoria.

– ¿Por qué no 3 nm en todas las variantes?

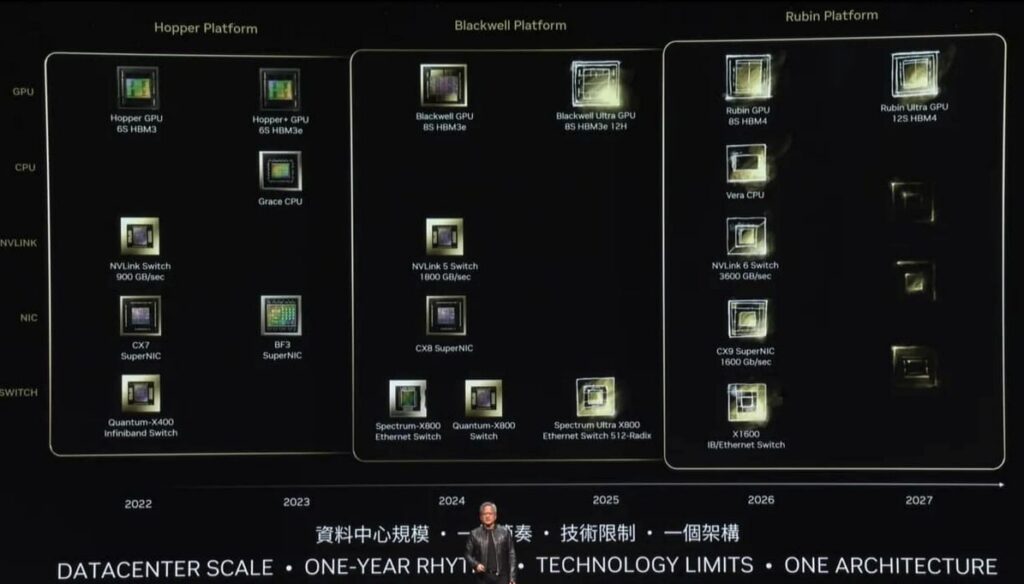

- A pesar de rumores, para ciertas piezas de Blackwell Nvidia ha mantenido 4N/4NP en lugar del salto a 3 nm, lo que se atribuye a riesgos de rendimiento/yield en grandes dies monolíticos y al uso de packaging avanzado. Eso no quiere decir que 3 nm no vaya a venir: la hoja de ruta de Nvidia contempla la microarquitectura Rubin, que sí utilizaría 3 nm.

La cadena de suministro: TSMC como pilar absoluto

– Capacidad y prioridad de Nvidia

- Según Digitimes, TSMC planea más que doblar su producción de packaging CoWoS (Chip-on-Wafer-on-Substrate) para 2025, y Nvidia se habría asegurado hasta el 60 % de esa capacidad.

- Un informe de Tom’s Hardware estima que en 2025 Nvidia podría consumir hasta un 77 % de las obleas de semiconductores dedicadas a IA.

- Para el nodo 3 nm, se reportó que TSMC elevó la producción hasta ? 160 000 oblea/mes para cubrir la demanda de Nvidia.

– Packaging y tecnología avanzada

- TSMC está totalmente “booked” con packaging avanzado: se estima que para fin de 2025, su módulo SoIC (chip-stacking) alcanzará 10 000 unidades/mes, mientras CoWoS alcanzará ~45-50k unidades/mes.

- Importante: Blackwell no solo es “un gran chip”, sino que su rendimiento depende tanto del silicio como del empaquetado avanzado (links de alta velocidad, retícula múltiple, etc.).

– Por qué esta alianza importa

- Huang, en su discurso en TSMC, no estaba solo agradeciendo: estaba poniendo la insuficiencia de otro modelo de producción (fabless + fundición “cualquiera”) frente a una alianza estratégica profunda.

- TSMC no es solo un “proveedor”, es más parecido a un socio de ingeniería y producción clave que decide, prioriza y optimiza para un número muy reducido de clientes estratégicos — y Nvidia es el primero.

- Este nivel de prioridad explica por qué Nvidia obtiene antes los nodos punteros, la capacidad de wafer y packaging, incluso frente a gigantes como Apple o AMD.

Relación estratégica entre Nvidia y TSMC: más allá del cliente-proveedor

– 38 años de evento, 30 años de relación

- En su discurso, Huang rememoró que “hace 38 años, TSMC era una startup; hace 30 años, Nvidia también lo era… y sin ustedes (TSMC) no habría Nvidia”.

- También rindió homenaje a Morris Chang, fundador de TSMC, al decir que “él fue quien me invitó a visitar TSMC en Taiwán hace tres décadas…”.

- Este tipo de narrativa no es habitual en el mundo corporativo: mezcla emoción, personalización y técnica. Eso conecta con el público geek que sigue “cómo se fabrican los chips”.

– Implicaciones de negocio

- Esta relación privilegiada permite a Nvidia acceder antes al metal, litografía, obleas y packaging que otros fabricantes que no tienen esa cercanía.

- Por otro lado, TSMC obtiene certeza de demanda, permite amortizar inversiones gigantes en fábricas de 3 nm/2 nm, packaging CoWoS/SoIC, etc.

- Es una win-win profundo que pocos actores en la industria tienen. De ahí esa frase de Huang “Sin TSMC, no habría Nvidia”.

Tecnología de fabricación, escalado y cuellos de botella

Litografía y yield

- TSMC ha sido pionera en la adopción de litografía ultravioleta extrema (EUV) en volumen, lo que ha posibilitado nodos avanzados como 5 nm, 4 nm, 3 nm.

- Para chips tan complejos como Blackwell, los retos de yield (rendimiento de obleas útiles) aumentan: cuanto mayor el área del die, mayor la probabilidad de defectos.

- Un dato clave: hubo un diseño de Blackwell que presentaba un “flaw” (fallo de diseño) que redujo el yield, y Huang reconoció que fue culpa de Nvidia y que TSMC ayudó a restablecerlo.

– Empaquetado avanzado (3D, multi-die)

- Blackwell no es solo una gran pieza de silicio: incluye múltiples dies interconectados (chiplets) y un enlace chip-to-chip de hasta 10 TB/s según fuentes.

- TSMC ofrece tecnologías como CoWoS y SoIC (stacking de dies) que permiten reducir latencias, aumentar ancho de banda y mejorar eficiencia energética. Estas son plataformas críticas para cargas de IA/ML.

- Debido a esto, aunque el transistor-count y el diseño sean clave, el packaging es cada vez más el “factor diferenciador” — y ahí TSMC tiene ventaja de primer nivel.

– Escalado de producción para IA

- Con la explosión de la demanda de IA generativa, Nvidia está acaparando obleas y packaging: que TSMC aumente producción a 160 000 wafers/mes para el nodo 3 nm apunta a que esta alianza está en modo “máquina de guerra”.

- Esto genera un efecto dominó: los competidores que no tengan esa prioridad pueden enfrentar cuellos de botella severos en obleas, packaging, memoria avanzada.

Impacto en el mercado, competencia y futuro inmediato

– Dominio del mercado de obleas IA

- Un informe cita que en 2025 Nvidia consumirá hasta el 77 % de todas las obleas destinadas a procesadores IA. Si esto se cumple, estamos ante un dominio sin precedentes.

- TSMC ya declara estar completamente “booked” en packaging avanzado hasta 2025. Quienes no tengan trato preferente podrían quedar fuera del “primer tren” de la IA.

– Rivalidades y qué está por venir

- La alianza Nvidia-TSMC pone presión directa sobre empresas como AMD, Intel, Apple: la “guerra de nodos” ya no es solo quién tiene el mejor silicio, sino quién tiene la mejor cadena completa (diseño + fundición + packaging + memoria).

- La microarquitectura Rubin (sucesora de Blackwell) apunta al 3 nm, lo que significa que esta carrera no ha hecho más que empezar.

Conclusión: Por qué este discurso importa más de lo que parece

El discurso de Jensen Huang en el evento de TSMC no fue un simple agradecimiento formal. Fue un acto simbólico con múltiples lecturas:

- Un reconocimiento público al papel esencial de TSMC en el éxito de Nvidia.

- Un guiño directo al ecosistema de fabricación global de semiconductores: no solo se trata de diseño, sino de producción a escala.

- Una señal de que Nvidia quiere hacerlo público: “no somos solo un cliente más”, sino el cliente privilegiado que define la hoja de ruta de la industria.

Déjanos tu opinión en los comentarios y únete a la discusión en Instagram, Facebook y YouTube.